Secure Processors Typical Computer Trusted Computing Base (TCB) Hardware Software Pary Ling3 App TRUSTED OS Leinel Ling Hypervuor BIOS TRUSTED DR CPV O INTWA 100's of millions of LOC, billions of losic getes!

Single-Chip Secure Processor Security micro aux monitor code

CPU DRAM NEWS

Untrusted OS, Memory, peripheral

- Shrink Software TCB

for thomsends of LOC.

Still trust the hardware

processor.

# Untrusted Memory CPU Dram Disk affacter: OS, physical access Confidentiality: Encryption Memory latency increase hurts performance memory (most programs are memory bottle necked!)

## Direct - Block Encryption Cipher Block Chaining (CBC) mode Cache Block B(2) Encyption

One-Time-Pad Encryption One-time-pad (OTP) encyption decryption otp [i]'s?

in writed DRAM

### Courter-Mode Encryption

Generate OTPs from timestamps With AES! Store timestamps with encrypted blocks in memory. L2- Cache-Writeback: 1. TS = TS+1 2. a. OTP = AESK (Addr, TS) b. EB = B D OTP 3. Write TS, EB to memory L2 - Cache - Miss: 1. Read TS from memory. Cache 2: in parallel of Read EB from Addr in Memory

TS's

An-child. 2: In parallel of Read EB from Addr in Memory

on-chip, 3. B= EB OTP

Speculate

Active Attacker/Integrity Just use a addrz EB MACCEB, addri) Untrusted DRAM Problem: Replay attacks Suppose progrem writes: EBI, MAC(EBI, addri) EB2, HAC(EB2, addr)

adversory ignores this write.

return this value on next read >

return this value on facture/detection.

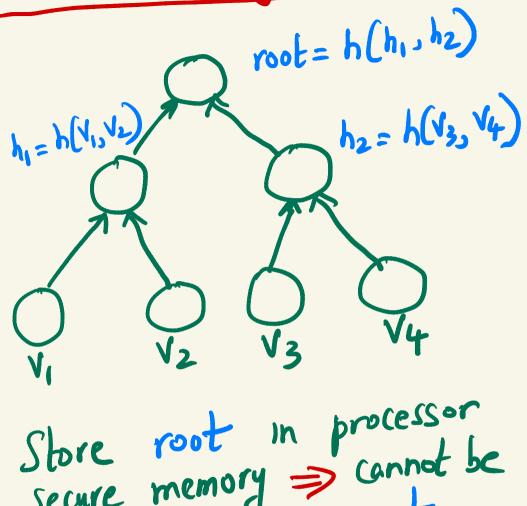

#### Merkle/Integrity Tree

Store root in secure memory = cannot be secure memory = cannot be tampered with. root tampered with wholeted checked on reads, wholeted on writes.

Tree Operations: Read Kead V3 Read V4 Compute  $h_2' = h(V_3, V_4)$ Check  $h_2' = h_2$ Read hi root' = h(h1, h2')

Compute root' = processor root

Check root' = processor root Adversory con't modify v3, v4, h2, h, to mutch not. Tree Operations: Write read h2 (hi, h2) = root Update processor root with root Caching intermediate hashes in trusted processor cache improves performance Significantly.

encryption 2 integrity verif. 13105 Hypervisor SGX enclave + MICROCOPE ROM cou ensures each EPC page belongs to exactly one enclave.

Shx Leaks - Untruoted OS/opp can attack

enclave via (shared) cache

timity attacks. - Address Translation Leak Virtuel > mappers) -> Physical address Page Tables

Untrusted OS manages its

and enclaves page tables.

Controlled -Channel Attack Paper Malicions

1. Hypervisor sets P (present) flog to 0 on all page table entries, lets enclave execute. First memory access causes a page facult. Hypervisor

maps foulty page & resumes

enclave execution. sees

enclave execution. page

Next page foult, hypervisor

maps in new page, and unmaps

normal mage 2. previous page, so it can see enclave's memory access pattern of page granularity (mmw affet) 4. Instruction execution > pages mapping

Ly gives control/secret data.

| S   | anctum Design                      |

|-----|------------------------------------|

| P   | artitioned Cache                   |

|     | Address                            |

|     | Tag Set offset                     |

|     |                                    |

|     | Set 0, Way 0 Set 0, Way 1 Enclave  |

| 4   | Set 1, Way 0 Set 1, Way 1] Enclare |

|     |                                    |

| (   | Set &-1, Wayo Set S-1, Way 1) OS   |

|     |                                    |

|     | OS menny                           |

| 247 | Enclave mem                        |

Janctum Design Page table isolation Physical Mem Enclave B Enclave A OS Region Virtuel addr Virtuel Addr space Host Enclose B Endave A Mac Liles Space EVPANCE EVENHE Enclare page tables (PTs) inside enclave memory (isolated from OS)

- need some hordware to multiplex PTs

### Enclave Life cycle (simplified)

| Untrusted OS<br>Enclave binary<br>image  |

|------------------------------------------|

| (i) (2) (3)                              |

| create enclave sealenclave               |

| grant resources seal enclare             |

| Load enclave                             |

| Security                                 |

| enter (5) monitor                        |

| Enclave exit enclave                     |

| 150loted memory, payetables, cache, etc. |

| Isolated memory space to the             |